# Small Signal Modelling of InGaAs/InAlAs pHEMT for low noise applications

<u>N. Ahmad</u> and M. Mohamad Isa School of Microelectronic Engineering, Universiti Malaysia Perlis, Pauh Putra Campus, 02600 Arau, Perlis, MALAYSIA. E-mail : norhawati@unimap.edu.my

*Abstract*—This paper presents the small signal modelling of high breakdown InP pseudomorphic High Electron Mobility Transistors (pHEMT) that have been developed and fabricated at the University of Manchester [1] for low noise applications mainly for the Square Kilometre Array (SKA) project. The ultralow leakage properties of a novel InGaAs/InAlAs/InP pHEMTs structure were used to fabricate a series of transistor with total gate width ranging from 0.2 mm to 1.2 mm. The measured DC and S-Parameters data from the fabricated devices were then used for the transistors' modelling. The transistors demonstrated to operate up to frequencies of 25 GHz. These transistors models are used in the design of Low Noise Amplifiers (LNAs) using fully Monolithic Microwave Integrated Circuit (MMIC) technology

Keywords— InGaAs/InAlAs; InP; pHEMT; Square Kilometre Array (SKA); LNA; MMIC

## I. INTRODUCTION

Nowadays, great progress has been made in the design and manufacture of InP based pHEMT devices particularly in low noise applications. This technology together with advances in MMIC technology, is driving future high volume, low cost, high performance millimetre-wave applications with high prospects [1]. The vital parameter for low noise that is cut-off frequencies  $(f_T)$  have been demonstrated in the THz range with this InP based pHEMT devices [2-4]. The unique and inherent properties of the carriers in a 2-DEG provide the device with high electron mobility and high sheet carrier density, making it the best device selection for many electronic applications. Recently, a novel strained InGaAs-InAlAs pHEMT devices having extremely high breakdown and low noise properties has been reported [5]. These devices show a great promise for use as a low cost high performance LNA for the intermediate frequency band of the SKA.

The MMIC manufacturing is time consuming and costly, since the correct functionality of the circuit can only be checked after the whole fabrication is completed. Therefore, an accurate small signal and large signal model of a device or transistor is an essential requirement for any circuit design either for Complementary Metal Oxide Semiconductor (CMOS) or HEMT technology before commencing the fabrication process. For that reason, there is a continuous effort from circuit designers to produce efficient transistor models since it was first developed by Curtice, 1980 [6]. A decade later, several empirical small signal and large signal models had been developed in

M. Missous Microelectronics And Nanostructures (M&N) Group, School of E&EE, The University of Manchester, M60 1QD, UNITED KINGDOM

| XMBE144                                                     | VMBE2100                                         |  |  |  |  |

|-------------------------------------------------------------|--------------------------------------------------|--|--|--|--|

| (Cap) In <sub>0.53</sub> Ga <sub>0.47</sub> As              | (Cap) In <sub>0.53</sub> Ga <sub>0.47</sub> As   |  |  |  |  |

| 50 Å                                                        | 50 Å                                             |  |  |  |  |

| (Barrier)                                                   | (Barrier) In <sub>0.3</sub> Al <sub>0.7</sub> As |  |  |  |  |

| In <sub>0.52</sub> Al <sub>0.48</sub> As 300 Å              | 300 Å                                            |  |  |  |  |

| δ-doped                                                     | δ-doped                                          |  |  |  |  |

| (Spacer)                                                    | (Spacer) In <sub>0.3</sub> Al <sub>0.7</sub> As  |  |  |  |  |

| In <sub>0.52</sub> Al <sub>0.48</sub> As 100 Å              | 100 Å                                            |  |  |  |  |

| (Channel)                                                   | (Channel)                                        |  |  |  |  |

| In <sub>0.7</sub> Ga <sub>0.3</sub> As 140 Å                | In <sub>0.7</sub> Ga <sub>0.3</sub> As 160 Å     |  |  |  |  |

| (Buffer)<br>In <sub>0.52</sub> Al <sub>0.48</sub> As 4500 Å | $(Buffer) In_{0.52}Al_{0.48}As 4500 Å$           |  |  |  |  |

| (Substrate) InP Fe                                          | (Substrate) InP Fe                               |  |  |  |  |

| doped                                                       | doped                                            |  |  |  |  |

Fig. 1: Two different epitaxial layer structures for device under test

order to allow the model being extracted to use Computer Aided Design (CAD) tools [7]. As significance, this research focuses on the characterization and accurate small signal modelling of advance material InP based pHEMT transistors using Advance Design System (ADS) Software.

## II. TRANSISTOR CHARACTERISTICS

In this work, a number of devices fabricated from two main types of epitaxial layer have been modelled for the use in low noise applications. The two different epitaxial layers are denoted as XMBE144 and VMBE2100. The effective gate length for all devices used in this study is 1  $\mu$ m while gate widths of the devices are ranging from 0.2 mm to 1.2 mm. All epitaxial layers were grown using The University of Manchester Molecular Beam Epitaxy (MBE) on RIBER V100H and V90H systems. These epitaxial layers were grown to improve the overall performance of the LNA through optimisation of the devices' epitaxial layers. Performance enhancement of XMBE144 and VMBE2100 was achieved through epitaxial layer improvements, resulting in low gate leakage and an enhancement in the devices' thermal stability. The epitaxial structures are shown in Fig. 1.

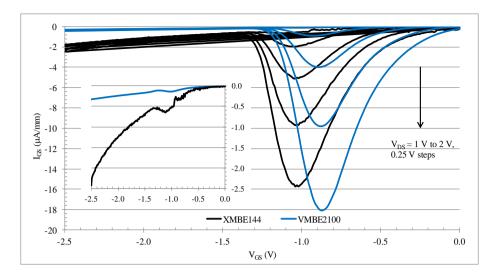

Fig. 2: On-state leakage current for XMBE144 and VMBE2100. Inset is the on-state leakage current of  $V_{DS} = 1 V$  (4 x 200  $\mu$ m devices)

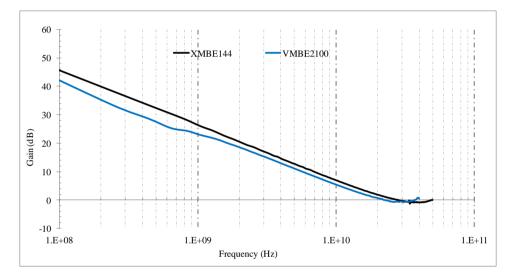

Fig. 3: Unity current gain (h21) plot versus frequency at VDS = 1 V. The  $f_T$  is obtained by the 0 dB crossing at x-axis (frequency)

The epitaxial structures of XMBE 144 and VMBE2100 share almost the same epitaxy layers and thicknesses. The only difference between these two materials is the Schottky Barrier layer for VMBE2100 is made from highly strained, high band gap (~2.1 eV) material, which is advantageous for achieving a higher Schottky barrier height, and consequently leads to a lower gate leakage current. Besides, the epilayers are made from  $\delta$ -doped structures to further enhance the carrier confinement in the quantum well, and additionally reduced the gate leakage. Fig.2 shows the on-state leakage current for XMBE144 and VMBE2100. It is obvious that the VMBE2100 device's leakage current is lower than XMBE144 through the adoption of wider band gap material as the Schottky barrier layer.

The cut-off frequency ( $f_T$ ) for these epilayers are ~ 25 GHz as depicted in Fig. 3, is among the highest has been reported for 1 µm devices.

This higher  $f_T$  performance is fundamental parameter for the devices' low noise characteristics as given by Fukui's minimum noise figure expression:

$$F_{min} = 1 + k_1 \frac{f}{f_T} \sqrt{g_m \left(R_s + R_g\right)} \tag{1}$$

## III. TRANSISTOR SMALL SIGNAL MODELLING

There are two techniques of device modeling; physical and empirical models. Both modeling can be used to represent a real device. The selection of the appropriate model depends on the exact requirements of the particular application since each techniques has its own advantages and limitation. In this project, the empirical technique is used to model the fabricated InGaAs/InAlAs/InP pHEMTs transistor. The empirical modeling begins with the small signal model followed by large signal model. The small signal modelling phase starts with the extraction of extrinsic and intrinsic parameters from pinched and biased dependent S-parameter measurements, from which the initial small signal model is generated.

This model is then optimized by fitting the modelled and measured S-parameters data. This will consequently reduce the modelling error. Large signal modelling of the devices is then performed; the DC and RF data are extracted, modelled and optimized. After the large signal model has been optimized, the complete model is ready to be used in circuit designs. However, this paper only discusses the small signal model of fabricated transistors, as the large signal model will be reported soon.

# IV. RESULTS AND DISCUSSIONS

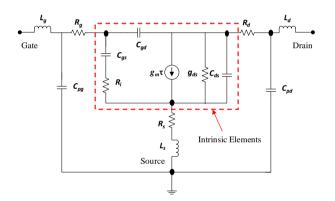

There are several small signal models circuit topologies described in [9-12]. The small signal model presented in this work, developed by Dambrine *et al.* [10], is the most commonly used. The most widely used equivalent circuit model for pHEMT/HEMT device is in Figure 4. The S-parameter measurements are firstly exported from the ICCAP

Fig. 4: Standard form of pHEMT/HEMT small signal equivalent circuit [64]

to the ADS software, where the small signal model is created. The configuration of the transistor's small signal model begins with the extraction of 8 extrinsic parameters, followed by the 7 intrinsic parameters. The extrinsic parameters are obtained from the device's pinched (cold) S-parameters measurement. This measurement is made when the device's channel is totally pinched, and it is bias-independent. Conversely, the intrinsic parameters extraction can be obtained from the bias dependent (hot) measurement. The extraction technique used throughout this project is an analytical method. The small signal model is performed to achieve an excellent fit between the modelled and measured data.

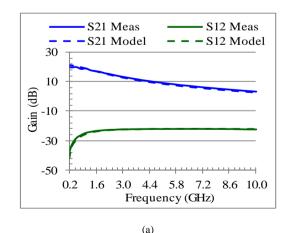

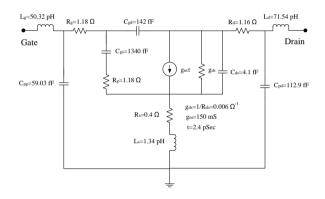

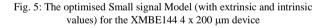

Fig. 5 shows the empirical model with the optimized extrinsic and intrinsic values for the XMBE144 4 x 200  $\mu$ m device. The S-parameter data is depicted in Figure 6, where the modelled data shows a good fit to the measured data up to a frequency of 10 GHz

TABLE I summarized the extrinsic parameters value while TABLE II summarized the intrinsic parameters value for devices involved in this work.

(b)

Fig. 6: The matched S-parameter data after Small signal Model optimisation for XMBE144's 4 x 200 µm device. (a) S21 and S12 and (b) S11 and S22

| TABLE I. | TABLE OF EXTRINSIC PARAMETERS FOR ALL DEVICES AT $V_{DS} = 1$ V and 10% $I_{DSS}$ |

|----------|-----------------------------------------------------------------------------------|

|----------|-----------------------------------------------------------------------------------|

| Sample ID | Gate fingers x<br>widths (μm) | C <sub>pg</sub><br>(fF) | C <sub>pd</sub><br>(fF) | <i>R</i> s<br>(Ω) | <i>R</i> <sub>g</sub><br>(Ω) | R <sub>d</sub><br>(Ω) | L <sub>s</sub><br>(pH) | <i>L<sub>g</sub></i> ( <b>pH</b> ) | <i>L</i> <sub>d</sub> ( <b>pH</b> ) |

|-----------|-------------------------------|-------------------------|-------------------------|-------------------|------------------------------|-----------------------|------------------------|------------------------------------|-------------------------------------|

| X         | 2 x 50                        | 7.8                     | 26.6                    | 5.80              | 1.94                         | 2.91                  | 8.1                    | 20.5                               | 17.9                                |

| XMBE144   | 2 x 100                       | 13.7                    | 37.9                    | 1.99              | 1.44                         | 1.38                  | 3.9                    | 26.7                               | 56.1                                |

| 4         | 4 x 200                       | 59.0                    | 112.9                   | 0.40              | 1.18                         | 1.16                  | 1.3                    | 50.3                               | 71.5                                |

| VMBE2100  | 4 x 200                       | 40.1                    | 155.6                   | 0.53              | 1.56                         | 1.43                  | 2.0                    | 79.7                               | 111.6                               |

TABLE II. TABLE OF INSTINSIC PARAMETERS FOR ALL DEVICES AT  $V_{DS} = 1$  V and 10%  $I_{DSS}$

| Sample ID | Gate fingers x widths<br>(µm) | g <sub>m</sub><br>(mS) | τ<br>(psec) | R <sub>i</sub><br>(Ω) | <i>R</i> <sub>ds</sub><br>(Ω) | C <sub>gs</sub><br>(fF) | C <sub>ds</sub><br>(fF) | C <sub>gd</sub><br>(fF) |

|-----------|-------------------------------|------------------------|-------------|-----------------------|-------------------------------|-------------------------|-------------------------|-------------------------|

| X         | 2 x 50                        | 19                     | 1.71        | 9.42                  | 1318.9                        | 150                     | 1.7                     | 22                      |

| XMBE144   | 2 x 100                       | 50                     | 1.77        | 3.89                  | 681.3                         | 410                     | 2.6                     | 43                      |

|           | 4 x 200                       | 150                    | 2.40        | 1.14                  | 157.9                         | 1340                    | 4.1                     | 142                     |

| VMBE2100  | 4 x 200                       | 170                    | 1.17        | 2.42                  | 179.0                         | 1400                    | 3.0                     | 150                     |

From the TABLE I, one can see that the capacitance values increase as the total device width is increased. Since the capacitance value is proportional to the contact area, the capacitance increases as the contact pad areas become larger. It can also be seen from TABLE I, that the terminal resistances are also reduced as the device size is increased. As the gate width is increased, the total gate area will increase, and consequently it will decrease the terminal resistances.

The intrinsic parameters follow the same trend as the extrinsic values as the device width is increased. However, a significant reduction in  $R_{ds}$  values can be observed as the device width is increased. This resistance can also be viewed as the resistance in the channel between the Drain and Source

terminals. As the device width is increased, the total area involved in parallel with the device width will be increased, and consequently the channel resistance is reduced.

## V. CONCLUSION

A small signal model for InGaAs/InAlAs/InP pHEMT is successfully presented. The model has been tested for a series of 1  $\mu$ m InP based transistors [13]. The consistency in obtaining the excellent agreement between modelled and measured data over 10 GHz, verify and validate the analytical technique uses. Having the advantages of an extremely lower gate leakage current and high cut-off frequency,  $f_T$  make the proposed devices one of the primary choices for low noise application, mainly for the SKA satellite [14].

## VI. ACKNOWLEDGEMENTS

This work has been supported by UK's STFC as part of the SKADS programme, Ministry of Higher Education and Universiti Malaysia Perlis.

## REFERENCES

- W.Haensch, et al., "Silicon CMOS devices beyond scaling" IBM J. Res. Dev., vol. 50, pp. 339-361, 2006.

- [2] K.Dae-Hyun and J. A. del Alamo, "30-nm InAs Pseudomorphic HEMTs on an InP Substrate With a Current-Gain Cutoff Frequency of 628 GHz," Electron Device Letters, IEEE, vol. 29, pp. 830-833, 2008.

- [3] H. Zirath, et al., "InP HEMTs and HBVs for Low Noise and Ultra-High Speed:Device and Circuit Research at Chalmers University of Technology.," presented at the Gallium Arsenide applications symposium. GaAs 2003, Munich, 2003.

- [4] R. Grundbacher, et al.,"High performance millimeter wave 0.1um InP HEMT MMIC LNAs fabricated on 100 mm wafers," in Indium Phosphide and Related Materials, 2004. 16th IPRM. 2004 International Conference on, 2004, pp. 284-287.

- [5] M. Mohamad Isa, D. Saguatti, G. Verzellesi, A. Chini, K.W. Ian, M. Missous, "Fabrication of novel high frequency and high breakdown InAlAs-InGaAs pHEMTs," in 8th International Conference on Advanced Semiconductor Devices & Microsystems (ASDAM), 2010, 25 27 Oct. 2010, pp. 41-44.

- [6] W. R. Curtice, "A MESFET Model for Use in the Design of GaAs Integrated Circuits," Microwave Theory and Techniques, IEEE Transactions on, vol. 28, pp. 448-456, 1980.

- H. Statz, et al., "GaAs FET device and circuit simulation in SPICE," Electron Devices, IEEE Transactions on, vol. 34, pp. 160-169, 1987.

- [8] A. J. McCamant, et al., "An improved GaAs MESFET model for SPICE," Microwave Theory and Techniques, IEEE Transactions on, vol. 38, pp. 822-824, 1990.

- [9] E. Arnold, et al., "Direct extraction of GaAs MESFET intrinsic element and parasitic inductance values," in Microwave Symposium Digest, 1990., IEEE MTT-S International, 1990, pp. 359-362 vol.1.

- [10] G. Dambrine, et al., "A new method for determining the FET smallsignal equivalent circuit," Microwave Theory and Techniques, IEEE Transactions on, vol. 36, pp. 1151-1159, 1988.

- [11] M. Y. Jeon and Y. H. Jeong, "An approach to extract extrinsic parameters of HEMTs," IEICE Transactions on Electronics, vol. E83-C, pp. 1930-1935, 2000.

- [12] K. Shirakawa, "Approach to determining an equivalent circuit for HEMT's," IEEE Transactions on Microwave Theory and Techniques, vol. 43, pp. 499-503, 1995.

- [13] M. Mohamad Isa, M. Missous, Y. Lai, J. Sexton, and S. Boulay, "Fabrication of Low Noise InAlAs-InGaAs pHEMT for SKA application (300MHz to 2GHz)", in UK Semiconductor 2011 Conference, The University of Sheffield, 6-7 July 2011.

- [14] N. Ahmad, M. Mohamad Isa and M. Missous, "Modelling, Design and Testing of novel InGaAs-InAlAs Low Noise Amplifier for Radio Astronomy applications", in UK Semiconductor 2012 Conference, The University of Sheffield, 4-5 July 2012